بسم الله الرحمن الرحيم

اليوم بفضل الله تعالي نتكلم بالتفصيل عن دوائر المازربورد

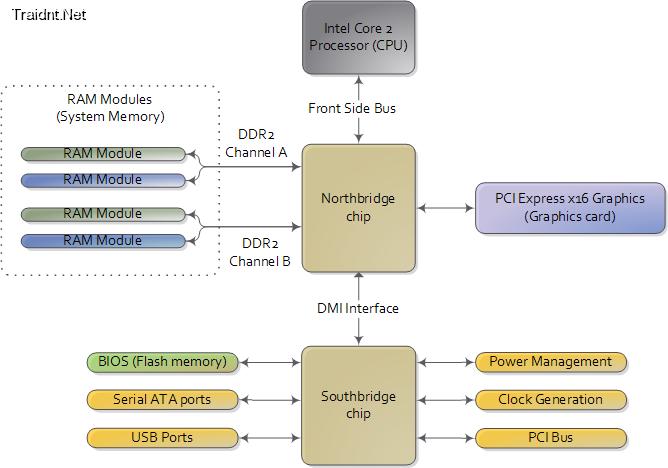

صورة مبسطة لدائرة المازربورد الانتل

اللوحات الأم التي تدعم منتجات إنتل

وكما هو واضح أن البرسسور لا يعالج أو تعامل مع الرام مباشرة (في حالة الانتل

فقط) ولكن يتم ذلك عن طريق northbridge ولهذا السبب تتوقف كفاءة اللوحة الأم

على كفائة تلك الشيب وهي الفيصل المهم في تحديد تميز لوحة أم عن أخرى.

- تتعامل الرمات مع البرسسور في تصميمات الإنتل عن طريق الجسر الشمالي (northbridge)

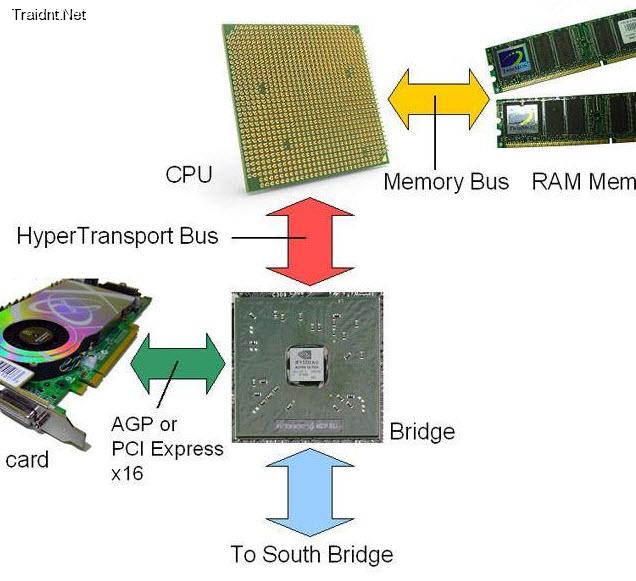

صورة مبسطة لدائرة المازبورد amd

اللوحات الأم التى تدعم AMD

كما هو واضح أن التحكم في الذاكرة (memory controller ) مدمج داخل المعالج لذا

لا توجد فروق كبيرة كما في حالة الانتل

- تتعامل الرمات مع البرسسور في تصميمات amd مباشرة دون المرور بالجسر الشمالي

وسنتطرق للعيوب التي تنتج في كل الحالتين عند التحدث عن دائرة الرامات

+ إنشاء موضوع جديد

النتائج 1 إلى 6 من 6

-

24-05-2016, 09:44 #1Status

- Offline

- تاريخ التسجيل

- Apr 2014

- الدولة

- Egypt

- المشاركات

- 4,642

Engineering and Technology

Engineering and Technology

- معدل تقييم المستوى

- 10

شرح شامل دوائــر المازربورد Motherboard Chipsets Map

------------------------------------------------------------------------

شرح شامل دوائــر المازربورد Motherboard Chipsets Map

------------------------------------------------------------------------

شركة رايز للهندسة و التكنولوجيا Rise Company for Engineering & Technology

------------------------------------------------------------------------

Web Hosting | Web Designing | E-Marketing

رقم # 1 فى خدمات الشركات Business Services

استضافة مواقع Web Hosting - عمل ايميل شركة Business Emails

تصميم موقع شركة Web Design - تسويق الكترونى على جوجل Google Adwords

www.rise.company | www.rise.company/emails

ملحوظة : جميع خدماتنا مخصصة للشركات فقط وغير متاحة للافراد

وليس لنا اى منتجات او صيانة نهائيا! يرجى الانتباه الى ذلك.

-

24-05-2016, 09:44 #2Status

- Offline

- تاريخ التسجيل

- Apr 2014

- الدولة

- Egypt

- المشاركات

- 4,642

Engineering and Technology

Engineering and Technology

- معدل تقييم المستوى

- 10

رد: شرح شامل دوائــر المازربورد Motherboard Chipsets Map

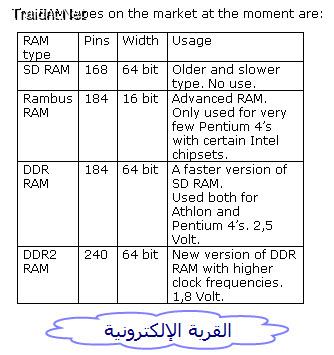

الرامات RAM

رد: شرح شامل دوائــر المازربورد Motherboard Chipsets Map

الرامات RAM

بداية من المعروف أن الرامات تعمل بنظام التزامن او ما يسمى TIMING وتخزن بها

البيانات على هيئة المصفوفة (MATRIX) بنظام يدعى STUCK

أو ما يطلق عليه في حالة الرامات FRIST INPUT FRIST OUTPUT )FIFO)

لذلك من المهم جدا أن تكون الرامات من نوع وسرعه واحدة حتى تعطي أقصى

توافق مع الجهاز.

ولكى نصل إلى الحالة القصوى لأفضل أداء للرمات يجب أن نهتم بما يسمى

DUAL CHANNAL إن كانت اللوحة الأم تدعم تلك الخاصية .

وهذا النظام من الرامات يجعل البرسسور يعمل بإمكانية أفضل لأنه من المعلوم أن

البرسسور أسرع بكثير من الرامات ولذلك ينتظر الرامات حتى تجلب الداتا وفي

فترات الانتظار لا يقوم البرسسور بأي وظيفه أو ما يطلق عليه حالة

IDALE .

لذلك هذا النظام يضاعف الاتصال بينthe memory controller and the RAM memory

أمثلة على شكل dual channal في اللوحة الأم

النوع الأول

النوع الثاني

وهناك العديد من الأشكال المختلفة.

الفولت الخاص بكل نوع من الرامات

كي نعرف مقدار الفولت اللازم لها ننظر على SLOT الخاص بها كما توضح الصورة التالية

أما في حالة RDRAM ( وهو نوع غير منتشر)

أما في حالة DDR3 الجديدة فيكون الفولت كما توضح الصورة

كيفية قياس فولت الرام على المازربورد

أولا المازربورد SDRAM

ثانيا المازبورد DDR1

ثالثا مازربورد DDR2

طريقة أخري لقياس الفولت لكل أنواع الرامات بغض النظر عن نوعها

يمكن قياس الفولت مباشرة على الرام وهي موجودة على المازربورد بقياسه على

الرجل رقم 1 في أيسي سوفت الرام نفسه.

اكواد الرامات على كارت التستر

C1 - C2 -C3 -C6 -C7 - dd

d1 -d2 -d3 -d4

------------------------------------------------------------------------

شركة رايز للهندسة و التكنولوجيا Rise Company for Engineering & Technology

------------------------------------------------------------------------

Web Hosting | Web Designing | E-Marketing

رقم # 1 فى خدمات الشركات Business Services

استضافة مواقع Web Hosting - عمل ايميل شركة Business Emails

تصميم موقع شركة Web Design - تسويق الكترونى على جوجل Google Adwords

www.rise.company | www.rise.company/emails

ملحوظة : جميع خدماتنا مخصصة للشركات فقط وغير متاحة للافراد

وليس لنا اى منتجات او صيانة نهائيا! يرجى الانتباه الى ذلك.

-

24-05-2016, 09:48 #3Status

- Offline

- تاريخ التسجيل

- Apr 2014

- الدولة

- Egypt

- المشاركات

- 4,642

Engineering and Technology

Engineering and Technology

- معدل تقييم المستوى

- 10

رد: شرح شامل دوائــر المازربورد Motherboard Chipsets Map

الجسر الشمالي (NORTHBRIDGE)

رد: شرح شامل دوائــر المازربورد Motherboard Chipsets Map

الجسر الشمالي (NORTHBRIDGE)

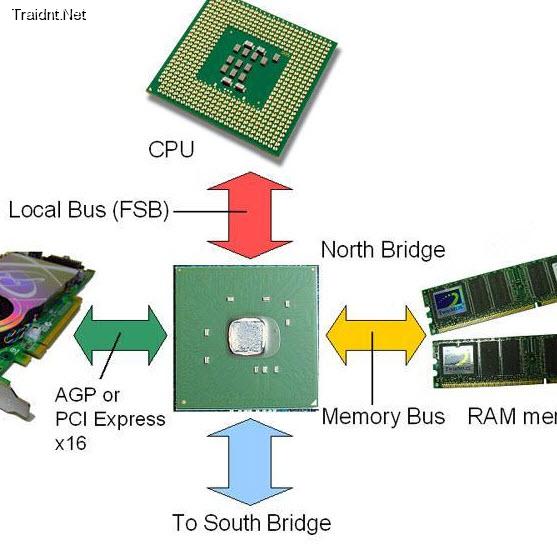

لو دققنا النظر في الصورة لوجدنا أن البرسسور يتصل بباقي مكونات البردة بواسطة ثلاثة طرق

memory address space

I/O address space

interrupts

كل ما يهمنا هنا في هذا المموضوع هو الرام والمازربورد.

نجد أن بوابة إتصال البرسسور بالمازربورد هي the front-side bus كما هو موضوح بالشكل فكل ما يحتاج البرسسور للقيام به من قراءة وكتابة (read or write memory)

إقتباس من موقع إنتل

اقتباس

It uses some pins to transmit the physical memory address it wants to write or read, while other pins send the value to be written or receive the value being read. An Intel Core 2 QX6600 has 33 pins to transmit the physical memory address (so there are 233 choices of memory locations) and 64 pins to send or receive data (so data is transmitted in a 64-bit data path, or 8-byte chunks). This allows the CPU to physically address 64 gigabytes of memory (233 locations * 8 bytes) although most chipsets only handle up to 8 gigs of RAM.

غالبا ما ننظر إالى الذاكرة على أنها الرام فقط فكل البرامج والعمليات من قراءة

وكتابة تتم من خلالها وكل الأوامر والعمليات التي يطلبها البرسسور من الرام تتم

من خلال الجسر الشمالي northbridge (هذا في حالة المازربورد الانتل) أما في

حالة المازربورد amd تتم مباشرة بين البرسسور والرام .

ولــــــــــكن هناك اتصال يتم عن ذاكرة تسمى Physical memory addresses هذه الذاكرة تقوم بعمل اتصال بين الأجهزة

المختلفة على اللوحة الأم هذا الإتصال يسمى ( memory-mapped I/O)

للمزيد من المعلومات عنه إضغط الرابط التالي

http://en.wikipedia.org/wiki/Memory-mapped_IO

الأجهزة التي يتم التوصيل بينها بواسطة ما يسمى Physical memory addresses هي :

video cards

PCI cards

BIOS

الجسر الشمالي (NORTHBRIDGE)

صورة تخطيطية لمكونات الجسر الشمالي الداخليه

يتم تنظيم busses في اللوحة الأم عن طريق مجموعة من المتحكمات (controllers) كما أنه توجد دوائر صغير تهتم بوظائف معينه مثل نقل الداتا من وإلى EIDE devices الهاردديسك على سبيل المثال.

عدد المتحكمات على اللوحة الأم يختلف على حسب عدد الأجهزة والهاردوير

المطلوب ربطة ببعضه على اللوحة الأم معظم وظائف هذه المتحكمات تم ربطها

ببعضها وتجميعها معا في زوجين من الشيبات هما northbridge & southbridge

ويتم التوصيل بين northbridge & southbridge بخط توصيل قوي يسمى link

كما توضح الصورة

تقوم northbridge بالتحكم في تتابع الداتا بين البرسسور والرام والفيجا.

ودوما نجد فوقها تبريد كبير large heat sink لتخفيف من درجة الحرارة الدخلية لها وينتج هذا الإرتفاع في درجة الحرارة من من الكمية الضخمة من الداتا التى تمر من خلالها

توضح الصورة الأجهزة والمخارج التى تتحكم فيها الشيب

AGP يعتبر كـــــ I/O PORT ويستخدم لكارت الشاشة وبالمقارنة مع الأخرين فهو

متصل مباشرة مع الشيب لأنة يحتاج أن يكون قريب جدا من الرام . ونفس الشىء

ينطبق على PCI Express البديل الجديد لل AGP في البرد الحديثه .

العيوب المشهورة التي تتسبب فيها NORTHBRIDGE

التهنيج

وهذا يحدث بسبب كثرة تدفق الداتا من خلالها وعدم مقدرة الشيب على التعامل

معها نتيجة SHORT أو OPEN أ في أحد الدوائر

الداخلية لها .

وينتج عن SHORT إرتفاع في درجة حرارة

الشيب و بعض البفات المحيطه بها شورت

وتعطي قيم تكاد تقترب من الصفر أما إذا قرأت

صفر واضح فهذا دليل أكيد على تلف الشيب

وينتج عن OPEN أن الشيب يكون درجة حرارتها

طبيعي أو باردة أكثر مما يجب وهذا من العيوب الصعبة التكهن بها.

عدم سخونة البرسسور

هذا عيب من أحد عيوب الشيب ويتسبب فيه الشيب نفسه أو موسفت تغذية

الشيب لا يقوم يإخراج القيم المطلوبة لتغذية الشيب .

تلف موسفتات Voltage Regulator بشكل

متكرر حتى بعد تغير الكنترولر .

فصل دائرة الرامات

وهذا عيب واضح ومشهور جدا أن تجد البردة تعطي عيب رام حتى مع سلامة دائرة

الرام وشحن البيوس أكثر من مرة (مشهور جدا في RZ و جيجا بيت 848).

نقص أو قطع لون من ألوان الشاشة

بهوت واضح في الشاشة أو ظهور الصورة كأشباح (لم يصادفني غير مرتين فقط)

والمزيد من العيوب التي نتتظرها من ردود الأعضاء

------------------------------------------------------------------------

شركة رايز للهندسة و التكنولوجيا Rise Company for Engineering & Technology

------------------------------------------------------------------------

Web Hosting | Web Designing | E-Marketing

رقم # 1 فى خدمات الشركات Business Services

استضافة مواقع Web Hosting - عمل ايميل شركة Business Emails

تصميم موقع شركة Web Design - تسويق الكترونى على جوجل Google Adwords

www.rise.company | www.rise.company/emails

ملحوظة : جميع خدماتنا مخصصة للشركات فقط وغير متاحة للافراد

وليس لنا اى منتجات او صيانة نهائيا! يرجى الانتباه الى ذلك.

-

24-05-2016, 09:49 #4Status

- Offline

- تاريخ التسجيل

- Apr 2014

- الدولة

- Egypt

- المشاركات

- 4,642

Engineering and Technology

Engineering and Technology

- معدل تقييم المستوى

- 10

رد: شرح شامل دوائــر المازربورد Motherboard Chipsets Map

الجسر الجنوبي South Bridge

رد: شرح شامل دوائــر المازربورد Motherboard Chipsets Map

الجسر الجنوبي South Bridge

الجسر الجنوبي يطلق عليه اسم ICH إختصاراً لـــــــ (I/O Controller Hub) .

يتحكم الجسر الجنوبي في أجهزة الإدخال والإخراج(controlling I/O devices) .

1-الهاردديسك سواء الداتا أو الساتا Parallel and SerialATA ports

-2بورت اليو اس بيUSB ports

3- كارت الصوت المدمج On-board audio

4- كارت الشبكة المدمج On-board LAN

5- فتحات البي سي أى PCI bus

6- مولد النبضات Real time clock (RTC)

-7 ذاكرة البيوس CMOS memory

On-board audio

في حالة وجود كارت الصوت مدمج بالبردة فإن التحكم فيه يكون عن طريق الجسر

الجنوبي (audio controller) وبالتالي يحتاج إلى شيب إضافي كي يعمل غالبا ما يطلق

عليه كودك ( codec= coder/decoder) .

On-board LAN

في حالة وجود كارت الشبكة مدمج بالبردة يحتاج كي يعمل إلى شب إضافي غالبا

ما يطلق عليه (phy= physical)

كذلك يتصل الجسر الجنوبي بإثنين من أهم الشيبات على اللوحة الأم وهما

1-البيوس (bios)

2-الخادم ( Super I/O chip) والتي بدورها

تتحكم في serial ports, parallel port and floppy disk drive.

ونجد أن تأثير الجسر الجنوبي في كفاءة اللوحة

الأم أقل من تأثير الجسر الشمالي لكن كما

ذكرنا فإن له تأثيرات على الأجهزة المتصلة به وعلى سبيل المثال الهارد ديسك كما أنه يعتبر مستقبل اللوحة اللوحة

حيث مداخل الإدخال والإخراج على سبيل المثال usb وغيره.

العيوب التي تتسبب فيها southbridge

كما توضح الصورة

بالإضافة إلى أعطال البور المشهورة في الشيبات sis و ati خاصة مع برد msi945

ومن العيوب المشهورة هو قيام البردة ور طبيعي مع سخونة شديدة في الشيب

وغالبا ما يتسبب فيه موسفت التغذية ويتم تغيرة مع العلم أنه يعطي قياس

سليم نظريا لكن علميا عدم قدرة الموسفت على منع مرور تيار التسريب

العكسي من الوصول للشيب وهو عيب مشهور في موديلات الجيجا بيت ما قبل

إصدار 865 خاصة rz

وعند تلف الشيب غالبا ما ترتفع درجة حرارتها بصورة كبيرة أو ينتج عنها شورت

على البفات المحيطة بها.

كذلك من دلائل أعطالها سخونة كبيرة في موسفت التغذية الخاص بها

سخونة كبيرة في مولد النبضات

------------------------------------------------------------------------

شركة رايز للهندسة و التكنولوجيا Rise Company for Engineering & Technology

------------------------------------------------------------------------

Web Hosting | Web Designing | E-Marketing

رقم # 1 فى خدمات الشركات Business Services

استضافة مواقع Web Hosting - عمل ايميل شركة Business Emails

تصميم موقع شركة Web Design - تسويق الكترونى على جوجل Google Adwords

www.rise.company | www.rise.company/emails

ملحوظة : جميع خدماتنا مخصصة للشركات فقط وغير متاحة للافراد

وليس لنا اى منتجات او صيانة نهائيا! يرجى الانتباه الى ذلك.

-

24-05-2016, 09:49 #5Status

- Offline

- تاريخ التسجيل

- Apr 2014

- الدولة

- Egypt

- المشاركات

- 4,642

Engineering and Technology

Engineering and Technology

- معدل تقييم المستوى

- 10

رد: شرح شامل دوائــر المازربورد Motherboard Chipsets Map

Super I / O

رد: شرح شامل دوائــر المازربورد Motherboard Chipsets Map

Super I / O

Super I/O chipset does your system health check.

دائرة Super I / O ويطلق عليها كثير من الأسماء مثل

- دائرة الإخراج والإدخال

- الخادم

- السكرتير

- منظم اشارة الجهد

- حساس الحرارة

- مؤشر الصحة العامة للبردة

وغيرها الكثير

الأجهزة التي يتحكم فيها Super I / O

- الفلوبي ديسك

- منفذ ps/2

- منفذ السيريال

- paralle port

كذلك يتحكم في الفولت الواصل لفانة البرسسور والتحكم في سرعة الدوران

يتحكم ايضا في اشارة 3ز3 فولت والتي بدورها تتحكم في power on /off

يتحكم في درجة حرارة البردة ككل

يتحكم في 5 فولت الواصله للمخارج في بعض البرد مثل soltek 848 عن طريق ايسي 8 رجل بجواره

يتحكم في تردد pci

يتحكم في الفرونت بنل أو بمعنى أدق الليدات الخاصة بالجهاز

- LPC (Low Pin Count) Interface

- Hardware Monitor Controller

- Fan Speed Controller

- Flash-ROM Interface

- SmartGuardian Controller

- IEEE1284 Parallel Port

- Floppy Disk Controller

- Game Port

- 56 General Purpose I/O Pins

- » Input mode supports switch de-bounce

- » Output mode supports one set of programmable LED blinking periods

- Watch Dog Timer

- » Times out the system, based on a user-programmable time-out period

- » Time resolution 1 minute, maximum 255 minutes

- Dedicated Infrared pins

- » Compliant with IrDA 1.4 for VFIR

- Single 48MHz Clock Input

- Single 3.3V Power Supply

- 128-pin LPQF

مزيد من التفاصيل في الصورة التاليه

------------------------------------------------------------------------

شركة رايز للهندسة و التكنولوجيا Rise Company for Engineering & Technology

------------------------------------------------------------------------

Web Hosting | Web Designing | E-Marketing

رقم # 1 فى خدمات الشركات Business Services

استضافة مواقع Web Hosting - عمل ايميل شركة Business Emails

تصميم موقع شركة Web Design - تسويق الكترونى على جوجل Google Adwords

www.rise.company | www.rise.company/emails

ملحوظة : جميع خدماتنا مخصصة للشركات فقط وغير متاحة للافراد

وليس لنا اى منتجات او صيانة نهائيا! يرجى الانتباه الى ذلك.

-

24-05-2016, 09:50 #6Status

- Offline

- تاريخ التسجيل

- Apr 2014

- الدولة

- Egypt

- المشاركات

- 4,642

Engineering and Technology

Engineering and Technology

- معدل تقييم المستوى

- 10

رد: شرح شامل دوائــر المازربورد Motherboard Chipsets Map

clock generator دائرة مولد النبضات

رد: شرح شامل دوائــر المازربورد Motherboard Chipsets Map

clock generator دائرة مولد النبضات

هي دائرة تقوم بتوليد موجة تزامن (timming signal) وتقوم هذه الموجة أو النبضة بعمل ما يسمي تزامن للدوائر التي تعمل على

المازربورد نظرا لاختلاف تردد كل دائرة عن الأخرى.

وتتولد هذه الاشارة على شكل موجة مربعه بسيطة أو اكثر تعقيدا على حسب اللوحة الأم.

لمزيد من التفاصيل عن تلك الاشارة اضغط هنا

الموجة المربعه

مكونات دائرة التردد (clock generator)

الكرستالة من الكوارتز

http://www.qariya.com/modules.php?na...getit&lid=2216

http://www.qariya.com/vb/showpost.ph...65&postcount=5

وهي التي تقوم بوظيفه المذبذب الخاص بعملية توليد النبضة الأوليه ويساعدها في

ذلك دائرة بسيطة تتكون من l;et وملف غالبا وتسمى lc

ويحسب قيمة التردد الناتج منها بالقانون التالي

ثم تدخل الاشارة في مرحلة التكبير وبعد ذلك الي أيسي clock generator

والذي بدورة يقوم بتكبير وتوزيع الاشارة التي تتحكم في تردد كل من

- CPU

- FSB

- GPU

- RAM

يتصل مولد النبضات بالsouthchip منتجا نوعين من النبضات لكي يعمل الجهاز هما

- system clock frequency

- reset signal

يتحكم البرسسور في مولد النبضات عن طريق الشيب ويقوم بالتحكم فيه عن طريق control signal bus.

لذلك عندما يريد مولد النبضات تغير التردد النظام طبقا للأمر الوارد له من المعالج

يقوم بعمل تنشيط ل rest signal التي تقوم مباشرة بعمل تصفير لحظي للتردد

وتوليد التردد الجديد الذي يعادل ما ارسلة المعالج

للمزيد

اقتباس

a chipset, connected to the CPU, wherein the CPU communicates with a

peripheral of the computer main board through the chipset;

a clock generator, connected to the chipset, providing the chipset with a

system clock frequency for operating the computer main board, wherein the

CPU controls the clock generator through the chipset, and the clock

generator is controlled through a first control signal bus; and

a reset signal generator, connected to the chipset and controlled by the

CPU through the chipset, which provides the chipset with a reset signal,

wherein the reset signal generator is controlled through a second control

signal bus, such that when the clock generator needs to change the system

clock frequency according to a command from the CPU, the reset signal

generator activates the reset signal simultaneously for changing a clock

frequency of the peripheral from a current frequency to an intended

frequency with respect to the svstem clock frequency where the intended

frequency can be repeatedly reset until the intended frequency matches in

ratio to the system clock frequency and the reset signal remains

activation until the system clock frequency is completely changed to a new

setting.

6. The circuit of claim 5, wherein the circuit further comprises a status

latch for storing a status parameter set by the CPU as soon as the system

clock frequency is changed, wherein the set status parameter is retrieved

by the chipset from the status latch to determine a ratio of the system

clock frequency to a clock frequency of the peripheral after the computer

main board is restarted.

7. The circuit of claim 5, wherein the first control signal bus includes an

I2 C bus.

8. The circuit of claim 7, wherein the second control signal bus includes

an I2 C bus.

9. The circuit of claim 8, wherein the chipset comprises an I2 C bus

interface that is used by the CPU to control the clock generator and the

reset signal generator.

10. A method for switching system clock of a computer main board, the

method comprising:

providing a CPU;

providing a clock generator, for generating a system clock frequency;

sending out a command from the CPU to the clock generator to change the

system clock frequency;

sending out a reset signal from the clock generator as soon as the clock

generator starts to change the system clock frequency wherein the reset

signal resets a clock frequency of a peripheral from a current frequency

to an intended frequency with respect to the system clock frequency where

the intended frequency can be repeatedly reset until the intended

frequency matches in ratio to the system clock frequency, and

canceling the reset signal by the clock generator as soon as the system

clock frequency is changed to a new setting.

11. The method of claim 10, wherein the method further comprises providing

a status latch for storing a status parameter set by the CPU as soon as

the system clock frequency is changed, wherein the set status parameter is

retrieved by the chipset from the status latch to determine a ratio of the

system clock frequency to a clock frequency of the peripheral after the

computer main board is restarted.

12. A method for switching system clock of a computer main board, the

method comprising:

providing a CPU;

providing a clock generator, for generating a system clock frequency;

sending out a command from the CPU to the clock generator to change the

system clock frequency;

sending out a reset signal from a reset signal generator as soon as the

clock generator starts to change the system clock frequency, wherein the

reset signal resets a clock frequency of a peripheral from a current

frequency to an intended frequency with respect to the system clock

frequency where the intended frequency can be repeatedly reset until the

intended frequency matches in ratio to the system clock frequency, and

canceling the reset signal from the reset signal generator as soon as the

system clock frequency is changed to a new setting.

13. The method of claim 12, wherein the method further comprises providing

a status latch for storing a status parameter set by the CPU as soon as

the system clock frequency is changed, wherein the set status parameter is

retrieved by the chipset from the status latch to determine a ratio of the

system clock frequency to a clock frequency of the peripheral after the

computer main board is re

يلاحظ عندما يتلف مولد النبضات

سخونة عالية على سطحة الخارجي

سخونة على الجسر الشمالي

عدم إضاءة لمبه clk على التستر

------------------------------------------------------------------------

شركة رايز للهندسة و التكنولوجيا Rise Company for Engineering & Technology

------------------------------------------------------------------------

Web Hosting | Web Designing | E-Marketing

رقم # 1 فى خدمات الشركات Business Services

استضافة مواقع Web Hosting - عمل ايميل شركة Business Emails

تصميم موقع شركة Web Design - تسويق الكترونى على جوجل Google Adwords

www.rise.company | www.rise.company/emails

ملحوظة : جميع خدماتنا مخصصة للشركات فقط وغير متاحة للافراد

وليس لنا اى منتجات او صيانة نهائيا! يرجى الانتباه الى ذلك.

المواضيع المتشابهه

-

[عرض] تعلم صيانه المازربورد والهارديسك واللابتوب بشهادات معتمده من الخارجيه

بواسطة zahret el ferdaws في المنتدى رايز الإعلانات التجارية Rise Advertiseمشاركات: 0آخر مشاركة: 19-08-2013, 16:28 -

شامل فن التليل لققطنا رائع

بواسطة Aya Adel في المنتدى قسم الحيوان و النباتمشاركات: 1آخر مشاركة: 07-03-2011, 23:11 -

عبدة الشيطان ......شامل + صور

بواسطة Eng Amr Adel في المنتدى قسم الدين الاسلامىمشاركات: 0آخر مشاركة: 08-12-2009, 22:11

رد مع اقتباس

رد مع اقتباس

المفضلات